Procesory i układy graficzne już wkrótce będą trochę… jak tort. Nie, nie staną się słodkie. Nikt też nie zamierza wbijać w nie świeczek. Chodzi o warstwy. Obaj producenci komputerowych CPU idą w mniej więcej tym samym kierunku – celując w warstwową budowę przyszłych CPU. Szczegóły technologii Zen 3 3D V-Cache odsłoniło AMD.

Wcześniej pojawiały się spekulacje, że AMD rozważa wdrożenie technologii Foveros 3D na licencji Intela. Firma zdołała jednak opracować rozwiązanie Micro Bump 3D – o 1 mikrometr cieńsze niż “krzemowy tort” konkurenta. Wprawdzie na układy Zen 4 nie mamy co liczyć w tym roku, ale nie znaczy to, że AMD nie ma odpowiedzi na nadchodzące układy Alder Lake. Wiele da się osiągnąć modyfikując znaną dziś architekturę Zen 3. Odpowiedzią ma być właśnie warstwowa budowa.

Jeszcze na Computex AMD ogłosiło taki właśnie ruch – Zen 3 wzbogacony o technologię 3D V-Cache. Wówczas podano, że układy te powinny pojawić się na początku 2022 roku, co oznacza iż będą naturalną kontrą wobec Alder Lake. Teraz, podczas wydarzenia Hot Chips, AMD przedstawiło nieco więcej szczegółów na temat działania pamięci podręcznej 3D V-Cache oraz przyszłych metod układania elementów SoC w stosy 3D.

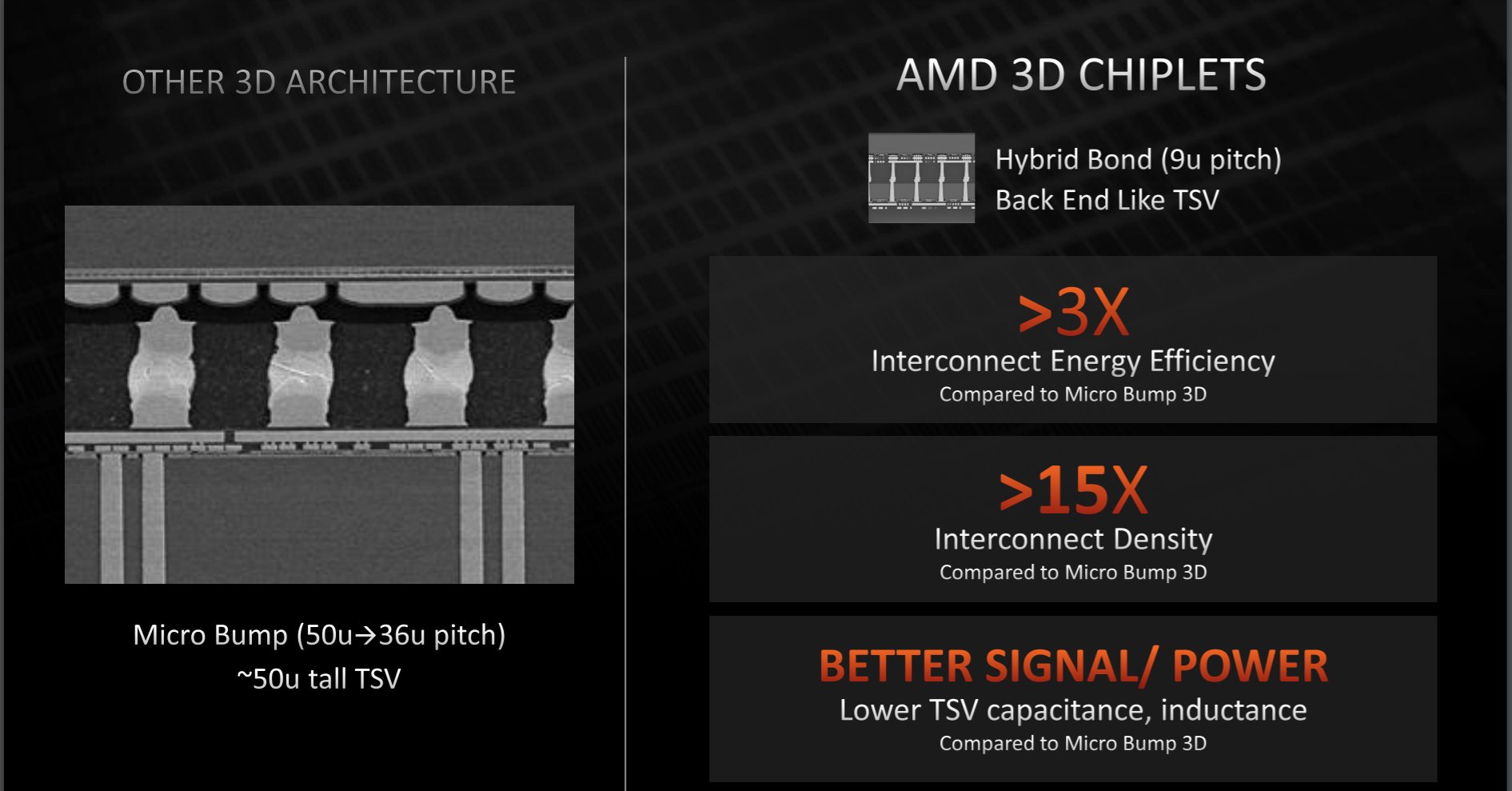

AMD chce zastosować 9-mikronowy pakiet chipletów Micro Bump 3D dla V-Cache z użyciem technologii TSV. Jest więc o 1 mikron cieńszy od stosów Foveros 3D firmy Intel, które będą używane do produkcji procesorów Alder Lake. Rzekomo Micro Bumps oferuje ponad 3-krotnie wyższą wydajność energetyczną interkonektów i 15-krotnie większą gęstość połączeń. Obecna technologia TSV, która działa jako pionowe połączenie między płytkami lub między matrycami, nie oferuje zbyt wielu wiązań, ale w przyszłości TSV ma być coraz bardziej wyrafinowany, umożliwiając bardziej złożone projekty układania w stosy 3D. Na przykład V-Cache umożliwia pełną komunikację krzem-krzem (DRAM na CPU lub CPU na CPU) poprzez bezpośrednie wiązania miedź-miedź. Umożliwia to dodanie 64 MB pamięci podręcznej L3 do istniejącej już pamięci wewnątrz chipletów, co ma zapewnić wzrost wydajności o 15% w grach i 19% w aplikacjach do tworzenia treści.

Lepsze rozstawy TSV pozwolą na bardziej skomplikowane techniki układania w stosy 3D, w tym IP na IP (rdzenie na rdzeniach / rdzenie na uncore). Zapotrzebowanie na energię również zmniejszy się w ten sposób, bo sygnał ma znacznie krótszą drogę do przebycia. Prawdopodobnie zobaczymy pierwsze zastosowanie techniki IP na IP z rdzeniami GPU RDNA2 ułożonymi na wierzchu rdzeni Zen 4. Chociaż na to, będziemy musieli zaczekać nieco dłużej.